Interview Questions

-

FV Interview Questions (II) – How to Do FSM Checks?

Jasper Gold offers “fsm_checks” command to auto-generate properties for FSM state / transition reachability. When running this command, the tool automatically detects FSM state variables or accepts user-specified FSM state variables, and extracts cover properties to prove. To define a conceptual FSM from the the…

-

FV Interview Questions (I) – How to Debug Unreachable Properties?

During formal verification, sometimes we may see unreachable properties. Using Cadence Jasper Gold for example, it can be flagged as either unreachable cover properties, or passing yet never triggered assert properties. This can be caused by over constraints, i.e., excessive assume properties, or design bugs.…

-

Why Should We Never Use Self-Determined Expressions in RTL?

A self-determined expression is the one whose bit length is solely determined by the expression itself. SystemVerilog LRM defines the bit lengths resulting from self-determined expressions. In the table below, i, j, and k represent expressions of an operand, while L(i) represents the operand i’s…

-

Hash Function and Its Applications: Hash CAM & Bloom Filter

A hash function defines the mapping relationship of (key, value) pairs. Good hash functions should be very fast to compute (easy for hardware implementation), and should minimize duplication of output values (less collisions). How to Implement a Hash Function? One common approach to implement a…

-

SCCB(Ⅲ) — Protocol Structure

We covered SCCB protocol signaling in previous post, and we will dive into the SCCB structure in this post. Below is the diagram of SCCB, it shows one master device connects to one slave device. Multiple slave devices can be connected to the same bus.…

-

Best Practice for Defining Configuration Registers

In the ASIC design industry, there are certain configuration register definition guidelines that RTL designers should follow. This is to achieve the following purposes: Guidelines for Configuration Register Content Guidelines for Configuration Register Address Map

-

Best Practice for RTL Naming Conventions

In this post, we share a few RTL naming conventions for better readability. See the table below. RTL Naming Convention RTL Naming Convention Use intelligible signal / variable names Better readability is achieved if the RTL code is “self-documented” Use “<name>_clk” for the name of…

-

SCCB (Ⅱ) — Protocol Signaling

After an overview of the SCCB protocol, we will dive into SCCB signaling in details. Below is the Pin description from the specification: Below waveform would help you to have a better understanding of the signal behavior during SCCB protocol data transmission.

-

Best RTL Coding Practice for Better PPA

Many times, different RTL coding styles in the same piece of code result in different PPA (Power, Performance, Area). Let us dive into a few examples. Use Register Enable Conditions When coding data pipelines, it is a good practice to always explicitly include an enable…

-

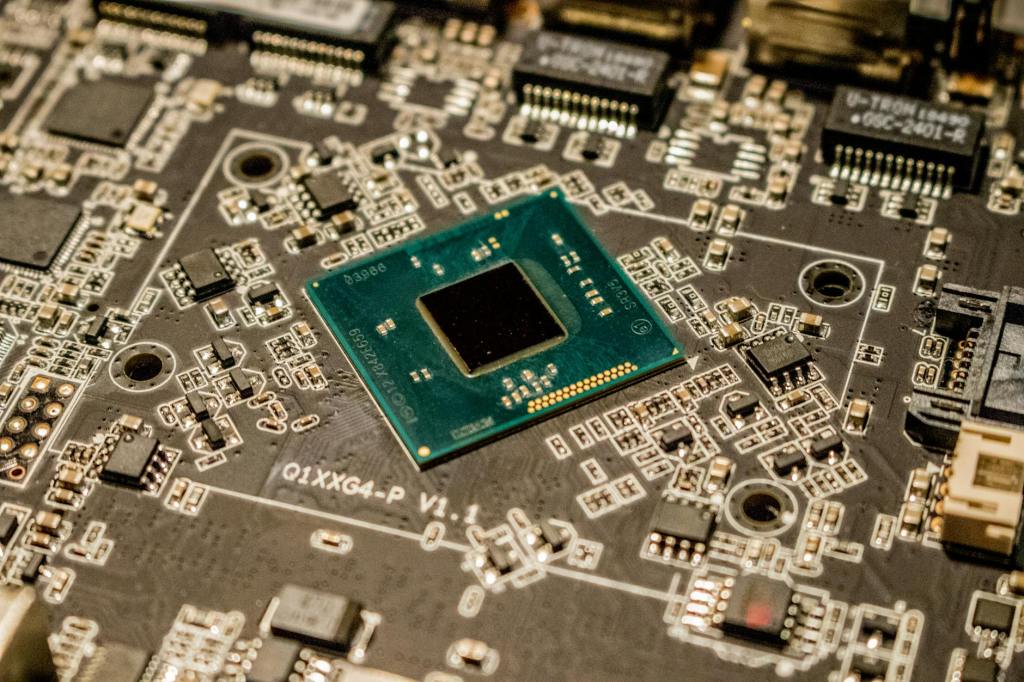

SCCB (I) — A Protocol in Image Sensor

Serial Camera Control Bus (SCCB) is defined and deployed by OmniVision Technologies, Inc. Most of the functions in OmniVision image sensors can be controlled by SCCB. The image sensor will be used as a slave device, and one master device will connect to at least…

Read Our Books for Free with Kindle Unlimited

Our books are available on Kindle Unlimited for free. Plus, you get unlimited access to hundreds of other books for preparing hardware interviews, including our recommended reading list

* Chipress participates in the Amazon Services LLC Associates Program, an affiliate advertising program designed to provide a means for sites to earn advertising fees by advertising and linking to Amazon.com

Subscribe

Enter your email to get updates from us. You might need to check the spam folder for the confirmation email.