It is not uncommon to see setup time and hold time conflicting in STA. It could be caused by:

- Large cell delay variations under different PVT conditions

- Large library setup time and / or hold time of certain type of cells

- Overly pessimistic setup time and / or hold time uncertainty

- Overly pessimistic setup time and / or hold time derating

- Short common paths of launch clock and capture clock, thus CRPR (Clock Reconvergence Pessimism Removal) does not get kicked in

Some timing paths may only face one factor, while the other paths may see multiple factors.

Timing paths with setup time and hold time conflicting can be categorized into 3 groups:

- Two timing paths have different start points, but the same endpoint. One timing path has setup time violation, while the other has hold time violation

- Two timing paths have the same start point and the same endpoint, and they traverse through different datapaths. One timing path has setup time violation, while the other has hold time violation

- A single timing path has both setup time and hold time violations

Group 1 and 2 are relatively easy to fix. Design engineers and STA engineers need to carefully analyze the timing paths, identify possible timing margins, and “move” the timing margins around. Group 3 is the most difficult one for timing fixes.

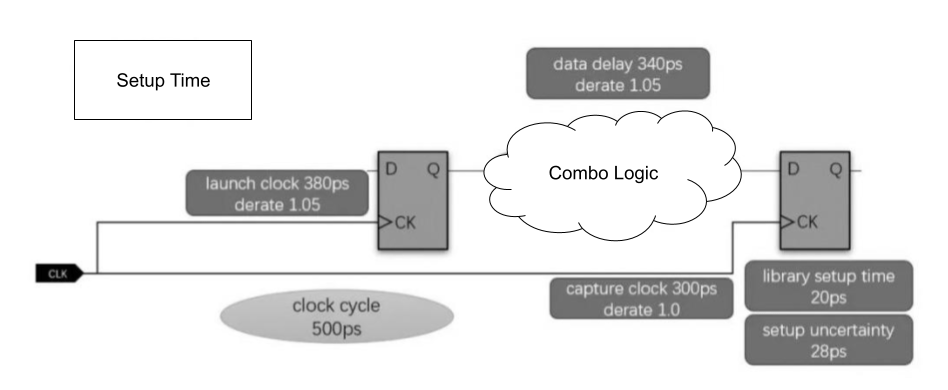

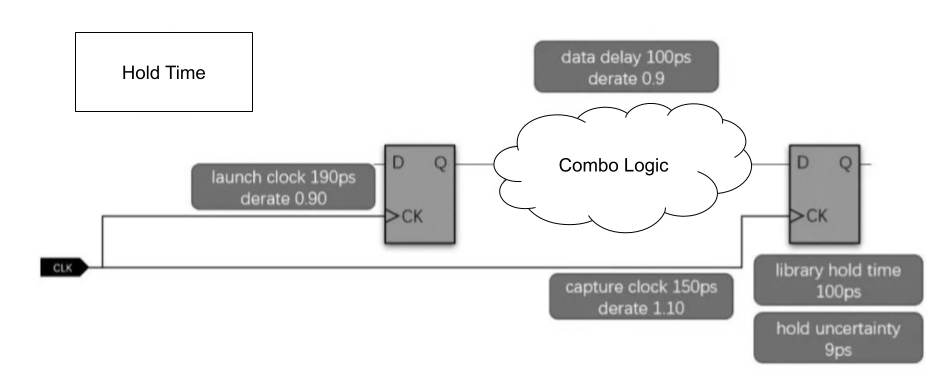

Assuming we have a timing path as shown in the diagram below:

Setup slack is calculated using the worst PVT conditions, and it is equal to (500 + 300 – 20 – 28 – 380*1.05 – 340*1.05) = -4ps.

Hold slack is calculated using the best PVT conditions, and it is equal to (190*0.9 + 100*0.9 – 100 – 9 – 150*1.1) = -13ps.

After thorough analysis, we can find that:

- Under different PVT conditions, clock path has a delay variation of 2, but datapath has a delay variation of 3.4

- There is no common paths of launch clock and capture clock, thus no CRPR exists

- Library flop hold time is huge (100ps)

- Best PVT corners / hold time corners have a much more pessimistic derating than worst PVT corners / setup time corners

For 1, we can replace the cells with the ones that have less variations across different PVT conditions.

For 2, we can improve / increase the common clock path of the launch clock and capture clock, and get CRPR kicked in. In our book “Crack the Hardware Interview – Physical Design and Silicon Debug”, we have a detailed example showing how CRPR improves both setup time and hold time slacks.

For 3, we need to check if the library hold time values have issues, and make sure we use the correct libraries.

For 4, derating at hold time corners is considered as timing sign-off constraints, and typically it cannot be changed.

Leave a comment